Notes on

Programming and Debugging 8051 with Edsim51

|

Topic |

|||

|

|

|

||

|

|

|

|

|

|

|

|

||

|

|

|

||

|

|

|

|

|

|

Description |

$ represents the address of the current instruction. |

|

|

Example |

Note: (For signed numbers) 02H – 04H = FEH |

#HIGH(…) , #Low(…)

|

Description |

#HIGH(…) represents the high byte of the address #LOW(…) represents the low byte of the address |

|

Example |

MOV DPH,#HIGH(table_of_number_to_7_segment_code) MOV DPL,#LOW(table_of_number_to_7_segment_code) table_of_number_to_7_segment_code: db 11000000B ; 0 = C0H db 11111001B ; 1 = F9H db 10100100B ; 2 = A4H db 10110000B ; 3 = B0H db 10011001B ; 4 = 99H db 10010010B ; 5 = 92H db 10000010B ; 6 = 82H db 11111000B ; 7 = F8H db 10000000B ; 8 = 80H db 10010000B ; 9 = 90H db 10001000B ; A = 88H db 10000011B ; B = 83H db 11000110B ; C = C6H db 10100001B ; D = A1H db 10000110B ; E = 86H db 10001110B ; F = 8EH |

|

Exercise |

After you run the instructions in the

example above, what will be the content of DPH and DPL? |

Addressable bits in RAM (e.g. 2FH.7)

|

Description |

The following examples show you how to program with the addressable bits. |

|

Examples |

SETB 2FH.0 SETB 78H ; The same as SETB 2FH.0 CLR 21H.7 CLR 0FH ; The same as CLR 21H.7 |

|

Definition |

A nybble = a half of a byte |

|

Example |

0110 1110 1100 contains 3 nybbles. |

|

Attribute |

An assembler directive |

||

|

Format |

ORG addr |

||

|

Description |

ORG is an assembler directive. It specifies a location in the code memory for the instruction below this directive. In other words, it directs the assembler to put the machine code of the subsequent instruction in the specified address. |

||

|

Example 1 |

Example 6 on the edsim51 website:

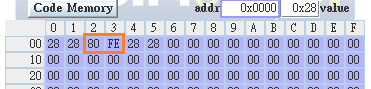

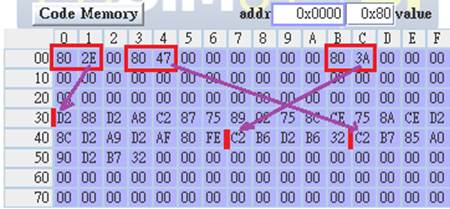

The machine code for Example 6 of the edsim51 website:

Note: (For signed numbers) 02H + 2EH = 30H, 05H + 47H = 4CH, 0DH + 3AH = 47H |

||

|

Example 2 |

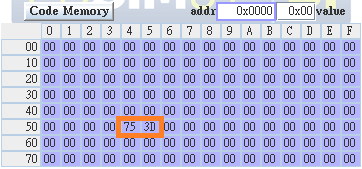

Using “ORG” to specify the locations for storing data in the code memory:

The corresponding machine code:

|

|

In edsim51, “ARn” and “Acc” are treated as offset.

They can be used

in instructions that contains an “offset” field. |

Some

examples are shown in the table below.

|

Example |

O/X (Correct

/ wrong) |

Instruction

Format |

|

CJNE A,R3,AGAIN |

X |

CJNE A,direct,offset |

|

CJNE A,AR3,AGAIN |

O |

|

|

PUSH R6 POP R6 PUSH A POP A |

X |

PUSH direct POP direct |

|

PUSH AR6 POP AR6 PUSH Acc POP Acc |

O |

|

|

ADD A,A |

X |

ADD A,direct ADD A,Rn |

|

ADD A,Acc ADD A,AR5 ADD A,R5 |

O |

|

|

INC AR4 INC R4 |

O |

INC direct INC Rn |

|

|

|

|

Below are some more

explanations.

|

Syntax |

Acceptable by edsim51: |

PUSH ARn POP ARn (n = 0, 1, 2, …, 7) |

||||||||||||||||||||||||||||||

|

Unacceptable by edsim51: |

PUSh Rn POP Rn |

|||||||||||||||||||||||||||||||

|

Explanation |

The machine code of PUSH:

The machine code of POP:

PUSh/POP can only use the direct addressing mode for their operand. Hence, it must be an 8-bit direct address of RAM, instead of a 3-bit encoding for registers. In edsim51, “ARn” stands for an 8-bit address, hence it is acceptable. On the other hand, “Rn” appearing in an assembly instruction implies the 3-bit encoding of registers, hence “PUSH/POP Rn” is not acceptable. |

|||||||||||||||||||||||||||||||

|

Example |

average:

PUSH PSW loop: ADD A, @R0 INC R0

DJNZ R1, loop

POP PSW |

|||||||||||||||||||||||||||||||

|

Similar cases |

|

|||||||||||||||||||||||||||||||

|

Summary |

|

|||||||||||||||||||||||||||||||

|

Attribute |

An assembler directive |

|

Format |

Using 0 Using 1 Using 2 Using 3 |

|

Description |

One of the four register banks is used for the registers R0 ~ R7. “USING “ is an assembler directive that indicates to the assembler which register bank is being used. |

|

Example 1 |

using 0 ; The register

bank 0 will be used. MOV R0,

#30H ; initialize the

subroutine by putting the start address into R0 MOV R1, #05H ; and by putting the size of the set into R1 CALL fillInNumbers CALL average_B JMP $ |

The End

To add

|

MOV B,#9H MOV A,#-5 ADD A,B MOV A,#0FBH ADD A,B MOV A,#-05H ADD A,B |

|

assembler directive: |

|

Topic:

How to specify a bit in the program? JB P1.3, AAA JB 93H,AAA JB 90H.3,AAA ; JB PSW.4,AAA ; Wrong JB 0D0H.4,AAA |

|

|

|

|