Question:

|

陳威呈 |

想請問關於期末考,如果是要填入uPM的內容時,該位元是don't care的話需要明確指出嗎,還是如果不影響到結果給0或1都可以算是對的,謝謝。 |

舉例來說對於指令MOV direct,A,此時ALU的Sel為don't care,不會影響結果,請問是可以隨機賦值或者是要寫成"-

- - " |

Ans:

|

Don’t care 必須以「–」 表示。例如2021Fall 的Q2:

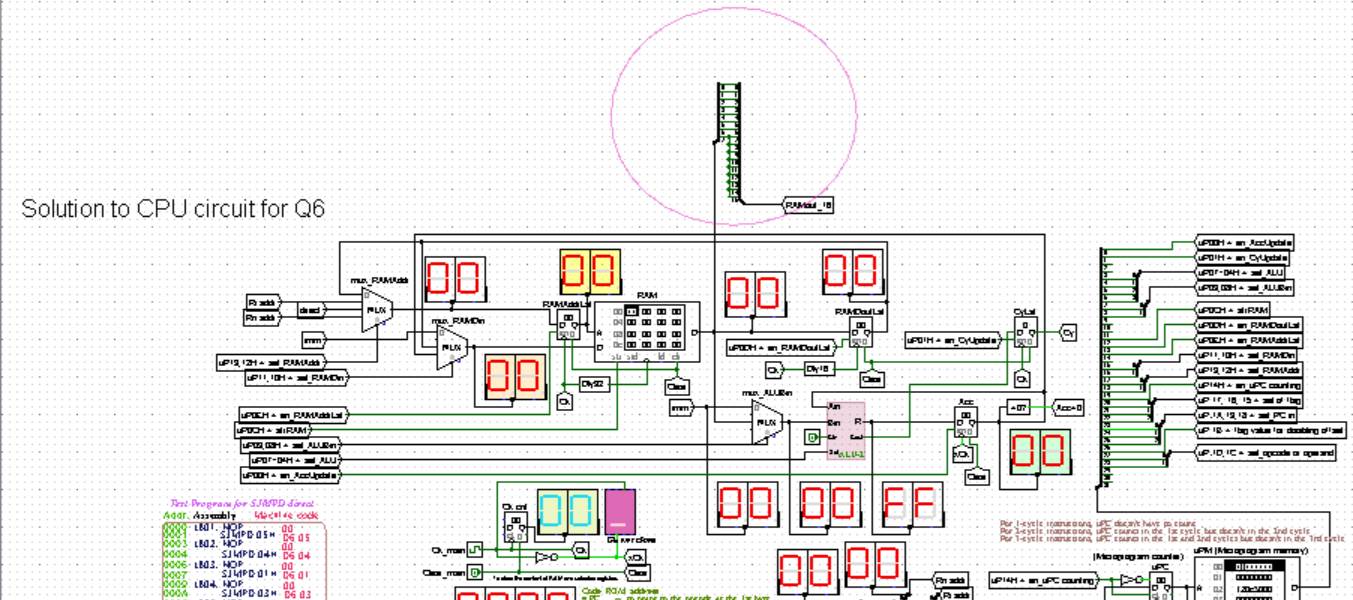

Please design the microinstruction for 『ROJMP Rn,offset』。 The circuit “9876543210陳小美Q1 solution.circ” is the teacher’s solution to Q1. Please

use this to design the microinstruction.

Solution:

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Question:

|

蔡雨蓁 |

想請問教授,在2021spring final exam Q6中提到 要修改電路去執行New

Instruction,在批改時要如何驗證電路的正確性,因每個人設計出的電路可能對應到不同的microinstructions,且題目未提到要輸入microinstructions |

Ans:

|

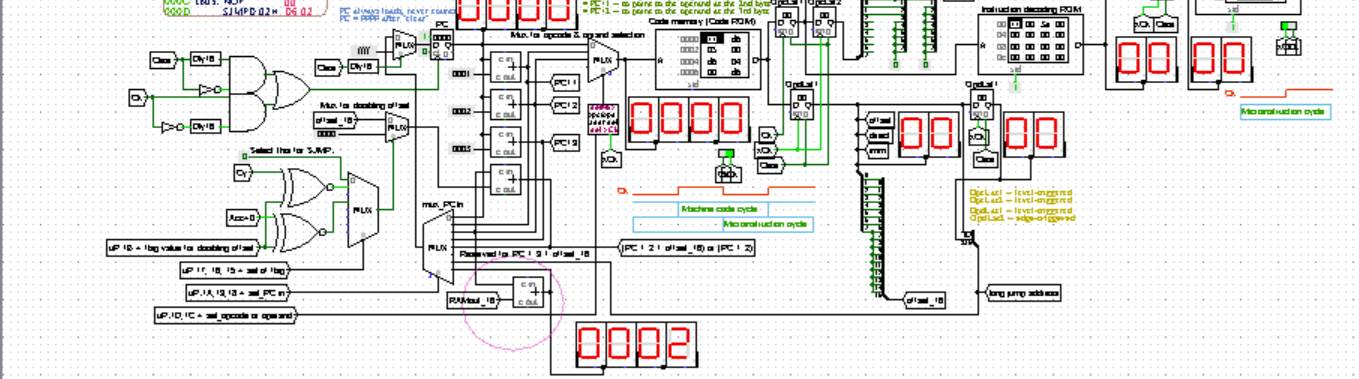

這一題的評分只看電路即知對錯。 你自己需要驗證的話,可以為該指令的microinstruction任選一個microprogram ROM的位址。 Q6. (15%) Circuit

Modification to Adopt a New Instruction 『SJMPD direct』 is a new assembly

instruction we will be designing in this final exam. Its function is to jump

to a location specified by an offset stored in the RAM. For example, if the RAM location 34H contains 08H,

then 『SJMPD 34H』 will fetch the offset 08H from the RAM location 34H and cause the

program execution to jump forward by 8 bytes. If the RAM location 34H contains F6H (i.e., -10 in decimal), then 『SJMPD 34H』 will cause the program execution to jump backward by 10 bytes. Please modify the circuit 9876543210 陳小美 Q6.circ so that the CPU circuit will be able to execute the 『SJMPD direct』instruction. Upload the circuit 9876543210 陳小美 Q6.circ after your modification. Note: The offset is 8-bit whereas the Code ROM

address is 16-bit, so the offset has to be

sign-extended to 16 bits before it is added to form a destination address. Note:

Please just modify the circuit hardware. At this stage we don’t have to worry about the microinstruction of 『SJMPD direct 』. Note: Please highlight your modification with

“highlight – big”, “highlight – medium”, or “highlight – small”, which can be

found in myLib-01. Solution:

|

Question:

|

鄭詠仁 |

請問even parity和odd parity是否能偵測出同時出現二個位元的傳送錯誤,如果不能,8051有別的方法能解決這個問題嗎 |

Ans:

|

1-bit parity check 可以偵測(detect)同時發生1, 3, 4, 7 bits

錯誤。對於偶數個bits 錯誤無法偵測。 |

Question:

|

李品賢 |

課程後面的8501 CPU design都是以Separate load and store ports的RAM為主,而沒有使用One load/store port。請問是只有以方便性為考量嗎(tri-state buffer can be removed)?還是有其他的考量? |

Ans:

|

RAM的形式不管是Separate load and store ports或是One load/store port,我們的CPU Design都可使用。 採用Separate的形式在電路的控制上比較簡單,而且比較容易了解。 若採用One load/store port形式,當然需要用到tri-state buffer,電路控制上比較複雜些。 其他方面的考量,例如bus的多寡,在我們目前的小電路上,重要性不明顯。 |

Question:

|

林延宬 |

μPM用來存所有微指令,想知道其內部指令越多是否代表其工作週期越長,會降低其速度? |

Ans:

|

「其內部指令越多是否代表其工作週期越長,會降低其速度?」 ------ 這句話應該部成立喔。 指令的數目應該不至於影響到執行速度。 |

Question:

Ans:

|

|

Question:

|

呂建霆 |

請問線上期末考的規定是否仍跟期中相同 |

eg:開書、可上網查詢等.... |

Ans:

|

|

Question:

|

蔣以新 |

期末考的模式會與去年一樣分三部分嗎? |

2021的模式與之前不太一樣,想問會繼續維持嗎? |

Ans:

|

|

Question:

Ans:

|

|

Question:

Ans:

|

|

Question:

Ans:

|

|

Question:

Ans:

|

|

Question:

Ans:

|

|

Question:

Ans:

|

|

Question:

Ans:

|

|